# QUEEN'S SCHOOL OF COMPUTING

# TECHNICAL REPORT

# Timed Automata to Synthesize Controllers of Dynamic Hierarchical Real-Time Plants

Md Tawhid Bin Waez, Andrzej Wąsowski, Juergen Dingel, Karen Rudie

August 28, 2016

# Timed Automata to Synthesize Controllers of Dynamic Hierarchical Real-Time Plants

Md Tawhid Bin Waez<sup>1</sup>, Andrzej Wąsowski<sup>2</sup>, Juergen Dingel<sup>1</sup>, and Karen Rudie<sup>1</sup>

Queen's University, Canada {waez@cs,dingel@cs,karen.rudie@}.queensu.ca

IT University of Copenhagen, Denmark wasowski@itu.dk

**Abstract.** We propose *Timed Process Automata (TPA)* for modeling and analysis of time-critical systems which can be open, hierarchical, and dynamic. The model offers two essential features for large industrial systems: (i) compositional modeling with reusable designs for different contexts, and (ii) automated state-space reduction technique. Timed process automata model dynamic networks of continuous-time communicating control processes which can activate other processes. We show how to automatically establish safety and reachability properties of TPA by reduction to solving timed games. To mitigate the state-space explosion problem, an automated state-space reduction technique using compositional reasoning and aggressive abstractions is also proposed. We use timed game theory and Uppaal Tiga in a couple of industrial case studies and in the development of TPA. Both the case studies show that state-space explosion is a severe problem for timed games. Suitable abstractions, however, dramatically improve the scalability of timed games in one case study. These case studies motivate the development of TPA and an automatable state-space reduction technique for them based on aggressive abstraction.

#### 1 Introduction

Automata are a prominent group of models in model-based development because they facilitate many important types of formal analyses. Finite automata (and their derived models, such as Kripke structures [1]) can be considered as the most popular, studied, and applied automata because of their rich theoretical properties and practicability. Properties of some systems, however, do not depend only on exact sequence of actions (or communication) but also the exact time of execution. Finite automata, implicitly, can model time information using sample timed data. For example, an action a that executes n seconds after the previous action b can be modeled as n special time tick symbols followed by a. Such implicit modeling of time can result in an exponential blowup of both input data and the size of the model. To avoid this problem, this paper uses timed automata (TA) [2,3], which can be viewed as finite automata with continuous clocks to record time. Timed automata are preferred to other real-time formal models (such as timed Petri nets [4], timed transition systems [5], and Modecharts ) because real-time reachability and some other important analytical properties

were first solved using symbolic semantics region graph of TA and after that other models adopted the same approach.

An open system continuously interacts with an unpredictable environment. A hierarchical system is a hierarchical composition of smaller systems. An automotive system, developed by an original equipment manufacturer (OEM), may be used in different models of cars. In this case, the system has a controller which helps the system adapt to different environments and cars. In other words, the system is an open system, which has two distinguished interacting segments: the controller and the environment. Typically, these systems consist of other smaller systems in a hierarchical structure. For instance, a system Actuator can be a component of a larger system Position, while Position can be a component of another system Brake-by-Wire, and so on. Every component of a system has a specific set of tasks; for example, system Brake-by-Wire may use its component Position to perform some desired tasks in interaction with the environment, and Brake-by-Wire may also indirectly—through using Position—use its sub-component Actuator to perform some desired tasks in interaction with the environment.

A dynamic hierarchical system is a hierarchical system whose components may change over time. Many hierarchical systems have dynamic characteristics, which are activating components only when needed. Dynamic behaviors are an important feature when resource constraints (such as limited memory) do not allow one to keep all the components active at the same time. Sometimes dynamic behaviors are inherent to the system. For example, we applied timed game theory in an industrial project to construct a fault-tolerant framework for a hierarchical open system that has a scheduler, a set of tasks, and a set of subtasks; only the scheduler is active in the initial system-state; subtasks are activated by their parent tasks, and the top level tasks are activated by their scheduler; thus the scheduler controls tasks, and a task controls its subtasks; due to the termination or the initialization of tasks (or subtasks) the structures of the processes may change; thus the system is a dynamic open system [6].

A ground hierarchical open system is a hierarchical (open) system that does not have a component. A non-ground hierarchical open system is a compound hierarchical open system. A ground hierarchical open system has a control hierarchy of depth 0. A compound hierarchical open system  $system_1$  has a control hierarchy of depth n+1, where n is the maximum of depths of the control hierarchies of the components contained in  $system_1$ . Many hierarchical open systems have  $system_1$  have  $system_2$  have  $system_3$  have  $system_4$  hierarchical open systems have  $system_4$  have components that are activated only when needed. Dynamic behaviors are an important feature when resource constraints (such as limited memory) do not allow one to keep all the components active at the same time. Models of industrial dynamic hierarchical open systems can be very detailed because of the hierarchical compositional bility. These details may introduce errors in the design and make automated analysis challenging.

Timed automata are desirable for the development of *open real-time systems* since TA can capture both discrete-time controllable behaviors of the system and dense-time uncontrollable behaviors of the environment. Timed automata have no explicit structured support for modeling dynamic hierarchical open systems. This

absence may lead to cumbersome design details in a large-scale system having several control hierarchies. Timed game automata [7,8,9]—a variant of TA—are a well-known model in the research community for the analysis of open dense-time systems. Dense-time formal methods of TA may provide the most accurate analysis, however TA, currently, are not suited for open systems in practice mainly because of poor scalability. This paper proposes the first compositional modeling with reuse and automatable-state-space reduction technique for the formal analysis of dynamic hierarchical open real-time systems. This paper applies TA to an industrial problem and proposes a novel variant TA together with a state-space reduction technique for the compositional modeling and analysis of dynamic hierarchical open real-time systems.

#### 1.1 Background

A timed automaton is a finite state automaton with a set of asynchronous nonnegative real valued *clocks* and a set of clock constraints. If a timed automaton is considered as a directed graph, locations represent the vertices of the graph, and locations are connected by edges. Locations of a timed automaton are graphically represented as circles. A clock valuation over the set of clocks is a mapping which assigns to each clock a nonnegative real value. An initial clock valuation maps each clock of a timed automaton to zero. The clock constraint which is associated with a location is called the local invariant of that location. Control can stay in a location only if the clock valuation satisfies the local invariant of that location. Local invariants are used to ensure the progress of the model [10], that is, control can stay in a location until its local invariant permits. An edge in a timed automaton is associated with a clock constraint, a subset of the clocks, and a label. The clock constraint which is associated with an edge is called the quard of that edge. An edge can be traversed only if the clock valuation satisfies the guard of that edge. Clock constraints are used to restrict the timing behaviors of the automaton. Each associated clock of an edge is reset to 0 when the edge traverses. At any instant, the value of a clock equals the time elapsed since the last time it was reset. While edges are instantaneous, time can elapse in a location. The semantic construction of TA is expressed using semantics objects called timed transition systems [11,9,3]. A timed I/O automaton [12,13,9] is a timed automaton which has an input alphabet along with a regular output alphabet. The controller plays controllable output transitions and the environment plays uncontrollable input transitions; thus timed I/O automata (TIOA) are a natural model for timed games. Two TIOA are composable with each other if they do not have a common output action.

**Definition 1** [11,9,3] A timed transition system (with only one initial location but without final location and  $\epsilon$ -transition) is a tuple  $\mathcal{T} = (St, s_0, \Sigma, \cdots)$ , where St is a set of states,  $s_0 \in St$  is the initial state,  $\Sigma$  is an alphabet, and  $\cdots$ :  $St \times (\Sigma \cup \mathbb{R}_{\geq 0}) \times St$  is a transition relation.

We use  $d \in \mathbb{R}_{\geq 0}$  to denote delay. A timed transition system satisfies time determinism (i.e., whenever  $s \stackrel{d}{\longrightarrow} s'$  and  $s \stackrel{d}{\longrightarrow} s''$  then s' = s'' for all  $s \in S$ ), time

reflexivity (i.e.,  $s \xrightarrow{0} s$  for all  $s \in S$ ), and time additivity (i.e., for all  $s, s'' \in S$ and all  $d_1, d_2 \in \mathbb{R}_{>0}$  we have  $s \stackrel{d_1+d_2}{\longrightarrow} s''$  iff there exists an s' such that  $s \stackrel{d_1}{\longrightarrow} s'$ and  $s' \stackrel{d_2}{\longrightarrow} s''$ ). A run  $\rho$  of a timed transition system  $\mathcal{T}$  from a state  $s_1 \in St$  is a sequence  $s_1 \overset{a_1}{\longrightarrow} s_2 \overset{a_2}{\longrightarrow} s_3 \cdots \overset{a_n}{\longrightarrow} s_{n+1}$  such that for all  $1 \leq m \leq n : s_m \overset{a_m}{\longrightarrow} s_{m+1}$  with  $a_m \in \Sigma \cup \mathbb{R}_{\geq 0}$ . A state s is reachable in a transition system  $\mathcal{T}$  if and only if there is a run  $s_0 \stackrel{a_0}{\longrightarrow} s_1 \stackrel{a_1}{\longrightarrow} s_2 \cdots \stackrel{a_{n-1}}{\longrightarrow} s_n$ , where  $s = s_n$ . Timed I/O transition systems are timed transition system with input and output modalities on transitions. Timed I/O transition systems are used to define semantics of TIOA. A constraint  $\delta \in C(X, V)$  over a set of clocks X and over a set counters, nonnegative finitely bounded integer variables, V is generated by the grammar  $\delta ::= x_m < q \mid k < \alpha \mid x_m - x_n < q \mid true \mid \Phi \land \Phi, \text{ where } q \in \mathbb{Q}_{\geq 0}, \ \alpha \in \mathbb{Z}_{\geq 0}, \ \{x_m, x_n\} \subseteq X,$  $k \in V$  and  $\langle \in \{\langle, \leq, \rangle, \geq \}$ . Consequently, the set of clock constraints C(X) is the set of constraints C(X, V), where  $V = \emptyset$ . Let  $\Psi(V)$  be the set of assignments over the set of variables V.

**Definition 2** [12,13,9,3] A timed I/O automaton is a tuple  $\mathcal{A} = (L, l_0, X, V, A, E, I)$ , where L is a finite set of locations,  $l_0 \in L$  is the initial location, X is a finite set of clocks, V is a finite set of counters,  $A = A_i \oplus A_0$  is a finite set of actions, partitioned into input actions  $A_i$  and output actions  $A_0$ ,  $E \subseteq L \times A \times \Phi(X, V) \times \Psi(V) \times 2^X \times L$  is a set of edges, and  $I: L \to C(X)$  is a total mapping from locations to invariants.

A clock valuation over X is a mapping  $\mathbb{R}_{\geq 0}^X: X \to \mathbb{R}_{\geq 0}$  and a counter valuation over V is a mapping  $\mathbb{Z}_{\geq 0}^V: V \to \mathbb{Z}_{\geq 0}$ . Given a clock valuation  $v \in \mathbb{R}_{\geq 0}^X$  and  $d \in \mathbb{R}_{\geq 0}$ , we write v + d for the clock valuation in which for each clock  $\bar{x} \in X$  we have (v+d)(x)=v(x)+d. For  $\lambda\subseteq X$ , we write  $v[x\mapsto 0]_{x\in\lambda}$  for a clock valuation agreeing with v on clocks in  $X \setminus \lambda$ , and giving 0 for clocks in  $\lambda$ . For  $\phi \in \Phi(X, V)$ ,  $v \in \mathbb{R}^{X}_{>0}$ , and  $n \in \mathbb{Z}_{\geq 0}^V$ , we write  $v, n \models \phi$  if v and n satisfy  $\phi$ . Let  $e = (l, a, \phi, \theta, \lambda, l')$  be an edge. then  $\overline{l}$  is the source location, a is the action label, and l' is the target location of e; the constraint  $\phi$  has to be satisfied during the traversal of e; the set of clocks  $\lambda \in 2^X$  are reset to 0 and the set of counters are updated to  $\theta$  whenever e is traversed.

**Definition 3** [13,9] Two TIOA  $\mathcal{A}^m = (L^m, l_0^m, X^m, V^m, A^m, E^m, I^m)$  and  $\mathcal{A}^n = (L^n, l_0^n, I^m, I^m, I^m)$  $X^n, V^n, A^n, E^n, I^n$ ) are composable with each other when  $A_o^m \cap A_o^n = \emptyset$ ,  $X^m \cap X^n = \emptyset$ , and  $V^m \cap V^n = \emptyset$ ; when composable, their composition is a TIOA  $\mathcal{A} = \mathcal{A}^m || \mathcal{A}^n =$  $(L^m \times L^n, (l_0^m, l_0^n), X^m \cup X^n, V^m \cup V^n, A, E, I), \text{ where } A = A_i \cup A_o \text{ with } A_o = A_o^m \cup A_o^n$ and  $A_i = (A_i^m \cup A_i^n) \setminus A_o$ . The set of edges E contains:

```

-((l^m, l^n), a, \phi^m \wedge \phi^n, \lambda^m \cup \lambda^n, \theta^m \cup \theta^n, (l'^m, l'^n)) \in E \text{ for each } (l^m, a, \phi^m, \theta^m, \lambda^m, l'^m) \in

```

and the set of invariants I is constructed as follows:  $I(l^m, l^n) = I^m(l^m) \wedge I^n(l^n)$

A real-time control problem can be viewed as a two-player timed game [7,14,15] between the controller and the environment, where the controller aims to find a

$<sup>\</sup>begin{split} E^{m} \ \ and \ (I^{n}, a, \phi^{n}, \theta^{n}, \lambda^{n}, l'^{n}) \in E^{n} \ \ if \ \ a \in \{A^{m}_{i} \cap A^{n}_{o}\} \cup \{A^{m}_{o} \cap A^{n}_{i}\} \\ - \ ((I^{m}, I^{n}), a, \phi^{m}, \lambda^{m}, \theta^{m}, (l'^{m}, I^{n})) \in E \ \ for \ each \ (I^{m}, a, \phi^{m}, \lambda^{m}, \theta^{m}, l'^{m}) \in E^{m} \ \ if \ \ a \notin A^{n} \end{split}$  $-((l^m, l^n), a, \phi^n, \lambda^n, \theta^n, (l^m, l'^n)) \in E$  for each  $(l^n, a, \phi^n, \lambda^n, \theta^n, l'^n) \in E^n$  if  $a \notin A^m$

strategy to guarantee that the system will satisfy a given property, no matter what the environment does [16]. An example of such reformulation is to find a strategy for the controller (or a reconfiguration service) to prevent the system from becoming unstable in the presence of the faults of the fault model. The *game reachability* problem is whether the system has a strategy to reach a target state regardless of how the environment behaves. The *game minimum-time reachability* problem in timed game automata is finding the minimum time required by the system to reach a target state regardless of how the environment behaves. Uppaal Tiga [17], a TIOA-based tool, is a tool for solving games based on timed game automata with respect to reachability and safety properties. Synthia [18] performs verification and controller synthesis for timed games.

#### 1.2 Motivation

The first goal of this paper is to develop an automatable synthesis technique for reconfiguration services for cost-effective fault tolerance. The next goal is to develop a TA-based modeling paradigm for dynamic hierarchical open systems, where a designer will not need to readjust a design for different compositions. However, the main motivation is to develop an automatable state-space reduction technique for TA-based analysis of dynamic hierarchical open systems.

Industrial multi-core systems typically use additional processing cores to provide fault-tolerance. Task-level reconfiguration techniques reduce the number of these additional processing cores—thus reducing costs—by reallocating the loads of the failed cores to the non-additional operational cores. The main challenge for developing a reconfiguration technique is to provide formal guarantee that the developed technique can handle all fault scenarios. Automated formal synthesis of such reconfiguration frameworks is highly desirable for industrial use.

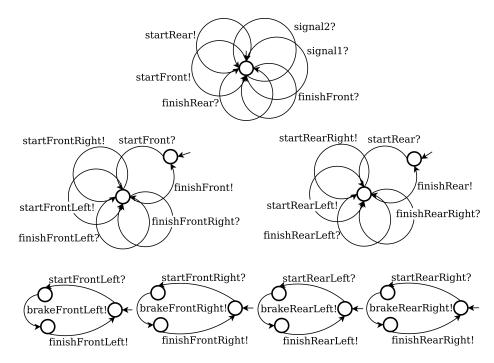

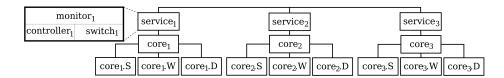

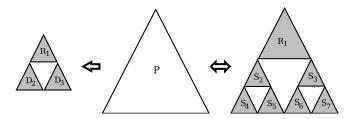

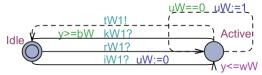

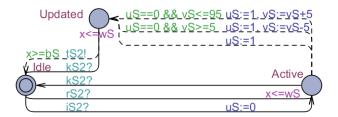

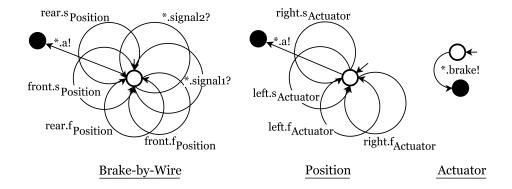

Figure 1 presents an abstract Brake-by-Wire system modeled using TIOA, and the system is developed by an OEM. The model has seven automata representing different copies of only three elements: one copy of the main thread of Brakeby-Wire (the top automaton), two copies of the main thread of Position (the two automata in the middle), and four copies of Actuator system (the four automata in the bottom). Each Position system contains two children (Actuator systems) and its main thread that schedules the children, communicates with its parent (the main thread of Brake-by-Wire), and performs some other functions, which cannot be performed by the children. Similarly, this Brake-by-Wire system contains two children (Position systems) and its main thread that schedules the children and performs some other functions, which cannot be performed by the children. In this model, the main thread of Brake-by-Wire is the root, which does not have a parent. However, in the future a car manufacturer may include this Brake-by-Wire system in a car and then the main thread of Brake-by-Wire will no longer be the root. Then a central control system may be able to start the main thread of Brake-by-Wire. To analyze the new complex system, a designer will need to manually alter the model again by including start and finish actions (in the top automaton of Figure 1). Let us assume a complex system contains N Break-by-Wire systems; to analyze this complex system, a designer will need

**Fig. 1.** An abstract Brake-by-Wire system modeled using standard TIOA, where one copy of the *main thread* of Brake-by-Wire (the top automaton), two copies of the main thread of Position (the two automata in the middle), and four copies of Actuator system (the four automata in the bottom)

to manually construct at least  $N \times 7$  automata with a proportionally growing alphabet! Existing TA-based modeling techniques do not support compositional modeling with reusable designs for different contexts; that is, a design may need to be altered manually in every composition. All these ad hoc alterations may make a large industrial design incomprehensible and error-prone.

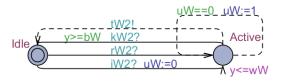

Fig. 2. The same Brake-by-Wire system of Figure 1 is modeled using TPA

Figure 2 contains the same Brake-by-Wire system of Figure 1 modeled by using our proposed *timed process automata (TPA)*, which always model a system only once. For example, Figure 2 presents only three TPA, which are equivalent to the seven automata of Figure 1. Moreover, the number of copies and the root status of Break-by-Wire system has no impact on the new design.

No automated state-space reduction technique has been developed for the analysis of dynamic hierarchical open dense-time systems. During our two projects with an automotive manufacturer, we noticed that even a (practically) very small real-time system may have a state space too large for automated formal analysis because of hierarchy, dynamic behaviors, and time calculations. We overcame the scalability problem in one of the projects—construction of a fault-tolerance framework in Section 2 and in [6]—by developing a manual state-space reduction technique that applies aggressive abstractions and uses fewer synchronizations. Applying this manual technique to a design of an industrial system is a challenging task. A generalized automated reduction technique, therefore, is needed for analysis of dynamic hierarchical open time-critical systems, which is provided by presenting an automatable reduction technique for TPA.

#### 1.3 Problem

The problem we address is to develop an automatable synthesis technique for reconfiguration frameworks using TA, and develop a theoretical foundation for TA 1) to allow compositional modeling with reuse for dynamic hierarchical open systems and 2) to allow timed games-based automatable analysis for large dynamic hierarchical open systems.

Challenges The main challenge is timed games-based synthesis has poor scalability. Moreover, for hierarchical compositional systems, the size of the composition in the monolithic analysis is exponential in the depth of the hierarchy of the system due to the product construction of the state space. Furthermore, the state space in the analysis is also linear in the product of the sizes of all included components of the system. The components of industrial hierarchical systems, unfortunately, typically are very detailed. For automatable reuse in compositional modeling, we need automatable techniques 1) to convert an independent system into a component of a larger system and 2) to construct n copies of component n of system system system n (such as n of system system, and the environment.

Scope Engineers of our industrial collaborator aimed to develop service-based solution for task-level reconfigurations to achieve fault tolerance for mixed-criticality multi-core systems. However, they were struggling to provide formal guarantee that the proposed services ensure fault tolerance. This paper synthesizes these services with formal assurance to solve their problem. Moreover, this sysnthesis process can be automated. Theoretically, TPA are not more expressive than timed game automata. For instance, on the semantic level TPA use timed

games for the analysis. However, TPA allow automatable analysis of larger dynamic hierarchical open systems. Timed process automata allow automated controlled safety and reachability analysis of arbitrary number of processes; but there is an implicit bound on the maximal number of active processes at a time.

**Organization** The paper concludes in Section 4 before that it provides:

- **Section 2** A novel automatable synthesis technique for reconfiguration services that assures fault tolerance of mixed-criticality multi-core systems.

- **Section 2.5** Results of experiments provide evidence of the usefulness of aggressive abstractions for state-space reduction.

- **Section 3.1** A TA variant called timed process automata that provides compositionality with reuse feature to model dynamic hierarchical open systems.

- **Section 3.2** An automated dense-time controllability analysis technique for the developed model.

- Section 3.3 An automatable state-space reduction technique for the developed automated controllability analysis, which will allow the analyses of larger dynamic hierarchical open systems.

- **Section 3.4** Results of experiments to determine effectiveness of the developed state-space reduction technique. The result provides evidence of the usefulness of the technique.

#### 1.4 Discussion

We propose TPA in Section 3. Resource constraints may not permit a hierarchical system to activate all of its components at the same time. Such resource constraints of can be modeled using TPA thus they are a variant of TA with resources [19]. Task automata [20,19] can model only two layers of hierarchy and only closed systems. Our proposed variant can model any numbers of hierarchies and can model both closed and open systems. Moreover, TPA can model private communication among components. Timed process automata are a member of the class of TA with succinctness [19]—such as TA with deadlines [21]— because they hide many design details from the designers to achieve succinctness. Timed process automata are also timed game automata [7,15,13,9] because the new variant uses timed games for analysis.

# 2 Synthesis of a Reconfiguration Service

We synthesize task-level reconfiguration services to ensure fault-tolerance of a mixed-criticality automotive system that consists of an asymmetric multi-core processor (AMP). The system has a fault-intolerant AMP scheduler. We augment the existing scheduler with supplementary reconfiguration services, which we synthesize. The services assure the periodic executions of all the critical tasks in the presence of faults from a fault model.

We use timed games at synthesis-time and lookup tables at runtime to provide task-level reconfiguration, a cost-effective fault-tolerance technique, for mixed-criticality multi-core systems. System-level requirements for embedded, real-time software in many domains (such as automotive) have enough flexibility to reallocate tasks from one processing core to another. A task-level reconfiguration technique reduces the number of redundant cores that are used only to provide fault-tolerance by reallocating the loads of the failed cores to the non-redundant operational cores. Reduction in the amount of expensive hardware gives task-level reconfiguration a hope to be a dominant fault-tolerance technique in the automotive industry, where cost-efficiency and fault-tolerance are both crucial issues. Since this economical technique can handle tasks with different levels of criticality, one of its prospective application sectors is next-generation automotive systems, most of which are expected to be mixed-criticality multi-core systems.

Formal methods have been used for the development of fault-tolerant real-time systems. However, in the industry, fault-tolerance problems are typically designed, analyzed, and solved using classical control theory [22,23]. Timed game theory [7,14,15], a dense-time automata-based game theory, is almost unexplored in the industry. The use of timed game theory to solve industrial problems is attractive because of automated controller synthesis, visual modeling, and dense-time formal analysis. Nevertheless, applying timed game theory to solve industrial problems is challenging because of its high computational complexity.

We use timed games to synthesize the embedded controllers of the reconfiguration services. Our approach guarantees fault-tolerance up to a certain maximal number of concurrent faults after inserting the services into the system. Such reliable and accurate information is very helpful to build mixed-criticality systems cost effectively. Intellectual property regulations do not allow us to present the case study on the systems of our industry partner. Instead we demonstrate the synthesis process using a small system, which is complex enough to show the essence of the problem and our approach, yet simple enough to allow a compact and comprehensible presentation.

Dense-time models can capture fault occurrences and other uncontrollable behaviors at dense-time, not only uncontrollable behaviors at discrete time. Timed automata have been used for many purposes [19] including for fault diagnosis [24,25,26], analyzing multi-core systems [27,28], task models [29], and analyzing mixed-criticality systems [30].

#### 2.1 Systems

We consider a class of multi-core systems having asymmetric processing cores. Different asymmetric cores may exhibit different performance for the same task. The systems under consideration are mixed-criticality systems, because they execute both critical tasks and non-critical tasks with two different priorities.

**Definition 4** A mixed-criticality system, of our consideration, consists of

- N asymmetric processing cores: core<sub>1</sub>, core<sub>2</sub>,  $\cdots$ , core<sub>N</sub>

- $-M tasks: task_1, task_2, \cdots, task_M$

- P critical tasks, where P < M

- A fault-intolerant criticality-unaware AMP scheduler with a static allocation of tasks

- load(task<sub>i</sub>, core<sub>j</sub>) is a function mapping each task-core pair to the worst-case load that the task generates on the core, represented as a number  $\{0,1,\cdots,100\}\cup\{+\infty\}$ , where +∞ represents incompatibility between the core and the task.

- Function  $primary(task_i)$  maps  $task_i$  to the core on which the task runs in the initial system-state

- Predicate critical(task<sub>i</sub>) holds only for critical tasks

- Each task is executed periodically. Tasks always terminate within the prescribed periods. Each task is described as a TIOA. These automata do not communicate<sup>3</sup>. Every task can be killed (and resumed) in any of its states by a reconfiguration technique.

- Fault Model: The system is fault-free in its initial system-state. In the other system-states, the system might suffer three types of faults: safety violations by tasks, permanent core failures, and temporary core failures. Critical tasks are assumed not to breach any safety constraints. Non-critical tasks may violate safety constraints. Every core of the system may fail. However, all cores of a system cannot simultaneously be in their failed states. The maximal number of cores that can fail concurrently is restricted by CFL, concurrent-failures-limit. No limit is imposed on the total number of fault occurrences in a run.

Given a mixed-criticality system of Definition 4, we want to obtain a task allocation policy that is able to cope with the failures admitted by the fault model. We will synthesize distributed reconfiguration services that assure uninterrupted executions of all the critical tasks. Section 2.2 explains how the reconfiguration technique is expected to work using an example.

#### 2.2 Task-Level Reconfiguration Service

We propose a service-based reconfiguration technique for the fault-tolerance of mixed-criticality systems, where the system has a task-level reconfiguration service for each core. The services manage critical tasks differently from non-critical tasks. Consider, for instance, a simple mixed-criticality AMP system system<sub>1</sub>, one of the systems that are described in Section 2.1. System system<sub>1</sub> executes six periodic tasks S, W, D,  $N_1$ ,  $N_2$ , and  $N_3$ . Only three tasks S, W, and D are the critical tasks, where in an execution S records exactly one update of a speedometer, and W (respectively, D) records at most one update of a wiper (resp., door). The system has three cores  $core_1$ ,  $core_2$ , and  $core_3$ , which are asymmetric but each core is able to execute all six tasks.

<sup>&</sup>lt;sup>3</sup> More generally, the communication can be abstracted by suitable understanding of worst and best case execution times, and terminations are independent of communication

Figure 3 presents a trace of a desirable behavior of system<sub>1</sub> in the presence of different faults after inserting the reconfiguration services; the figure omits suspended non-critical tasks to avoid clutter. At any given time, the periodic execution of a task can be assigned to at most one operational core. A task is assigned to its primary core in the initial systemstate, where a core is responsible to execute only its primary tasks. For instance, core<sub>1</sub> is the primary core of

| S <sub>1</sub>        | core <sub>1</sub> : operational S: primary N <sub>1</sub> : safe         | core <sub>2</sub> : operational<br>W: primary<br>N <sub>2</sub> : safe | core <sub>3</sub> : operational<br>D: primary<br>N <sub>3</sub> : safe |

|-----------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|

| $s_2$                 | core <sub>1</sub> : operational<br>S: primary<br>N <sub>1</sub> : safe   | core <sub>2</sub> : failed<br>W: primary<br>N <sub>2</sub> : safe      | core <sub>3</sub> : operational<br>D: primary<br>N <sub>3</sub> : safe |

| <b>s</b> <sub>3</sub> | core <sub>1</sub> : operational<br>S: primary<br>N <sub>1</sub> : safe   | core <sub>2</sub> : failed                                             | core <sub>3</sub> : operational<br>D: primary<br>W: backup             |

| $s_4$                 | core <sub>1</sub> : operational<br>S: primary<br>N <sub>1</sub> : unsafe | core 2: failed                                                         | core <sub>3</sub> : operational<br>D: primary<br>W: backup             |

| s <sub>5</sub>        | core <sub>1</sub> : operational<br>S: primary                            | core 2: failed                                                         | core <sub>3</sub> : operational<br>D: primary<br>W: backup             |

| s <sub>6</sub>        | core <sub>1</sub> : operational<br>S: primary                            | core 2: operational                                                    | core <sub>3</sub> : operational<br>D: primary<br>W: backup             |

| S <sub>7</sub>        | core <sub>1</sub> : operational<br>S: primary                            | core <sub>2</sub> : operational<br>W: primary<br>N <sub>2</sub> : safe | core <sub>3</sub> : operational<br>D: primary<br>N <sub>3</sub> : safe |

**Fig. 3.** Sample trace of system<sub>1</sub> with reconfiguration

task S, and S is a primary task of core, in Figure 3. We call a non-primary core a backup core of a critical task when that core can execute that task; similarly, a task is a backup task of its backup core. Whenever a core fails, the services assign the critical tasks that were previously assigned to that failed core to the operational cores. The services may kill and suspend temporarily one or more non-critical tasks on the operational cores during a reallocation process to ensure enough processing capacity for the reallocated critical tasks. In Figure 3, core core<sub>2</sub> fails in system-state s<sub>2</sub>; in the next system-state, the periodic execution of critical task W is assigned to a backup core core; and the periodic execution of non-critical task N<sub>3</sub> is suspended temporarily on core<sub>3</sub> to have enough processing capacity for W. A critical task is allowed to execute further on a backup core only if the primary core is in a failed state. The services kill a critical task on a backup core (if that task is initialized or released) and cancels the assignment of that task on that backup core, whenever the primary core recovers from a temporary failure. As an example, core core<sub>2</sub> recovers from a temporary failure in system-state s<sub>6</sub>, and after that only core<sub>2</sub> is assigned to perform critical task W. The services reinstate a suspended non-critical task as soon as enough processing capacity for that task is regained due to the recovery of a core from a temporary failure; for example, the periodic execution of non-critical task N<sub>3</sub> is reinstated in system-state s<sub>7</sub>. The services permanently suspend a non-critical task when it performs some harmful activities, such as illegal memory access. For instance,

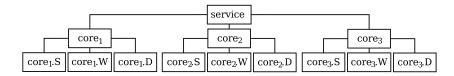

Fig. 4. Architecture of system<sub>1</sub> after adapting abstractions of Section 2.3

non-critical task  $N_1$  performs some harmful activities in system-state  $s_4$ , and the task is permanently suspended in system-state  $s_5$ .

Problem Statement Given a mixed-criticality system as specified in Definition 4, the problem is to synthesize a reconfiguration service service<sub>i</sub> for each core core<sub>i</sub> such that service<sub>i</sub>: (i) reacts whenever any other core fails or a core recovers (including core<sub>i</sub>), or a non-critical task violates a safety constraint on core<sub>i</sub>; (ii) at that time service<sub>i</sub> may kill, resume, and suspend any task running on core<sub>i</sub>; and (iii) as long as core<sub>i</sub> is in a failure state, none of its tasks nor service<sub>i</sub> executes. All reconfiguration services of a system together satisfy a property that at all times critical tasks are allocated to operating cores as long as the CFL limit is observed, and any non-critical task that has violated a safety constraint is suspended from execution indefinitely.

### 2.3 Modeling

We construct a timed game model of the system in a way that an unsafe location becomes reachable when a core exceeds its processing capacity. The model explicitly or implicitly captures the behaviors of the scheduler, the reconfiguration services, the cores, and the tasks.

To reduce complexity: (i) we model only a single (central) reconfiguration service for the whole system, instead of one service per core; (ii) we assume that every non-idle state of a task requires the worst-case core load of the task on the current core; and (iii) we abstract away the non-critical tasks. These three assumptions do not prevent synthesis of a distributed reconfiguration service per core, which will be shown in Section 2.4. Our model depends on four system parameters: (i) the release period of each task (constants pS, pW, pD); (ii) the worst-case load of each task on each core, in percent of the processing capacity of that core (constants 1S1, 1W1, 1D1, 1S2, 1W2, 1D2, 1S3, 1W3, 1D3); (iii) the worst-case execution time (WCET) of each task on all cores (constants wS, wW, wD); and (iv) the best-case execution time (BCET) of each task on all cores (constants bS, bW, bD).

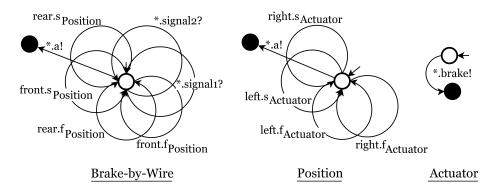

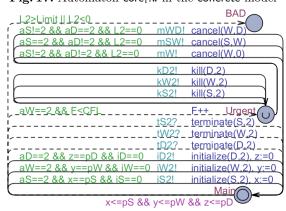

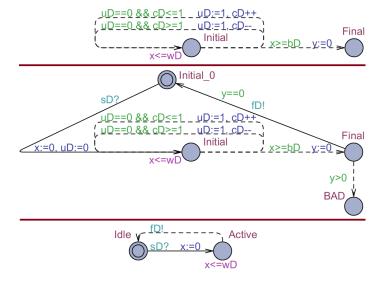

Now we illustrate the design process by constructing a concrete model of mixed-criticality AMP system  $\mathsf{system}_1$ . The main design principle behind this model is to describe each component of the system in detail as a TIOA then obtain an intuitive concrete model by composing all the components using parallel composition [9]. The concrete model has 13 TIOA, which follow five different templates. In general, the concrete model has at most  $(N \times K) + N + 1$  TIOA and

K+2 templates, where N is the number of total cores, K is the number of total critical tasks, constant 1 automaton for the central service, constant 1 template for cores, and constant 1 template for the central service.

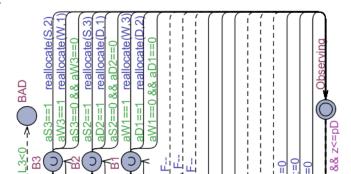

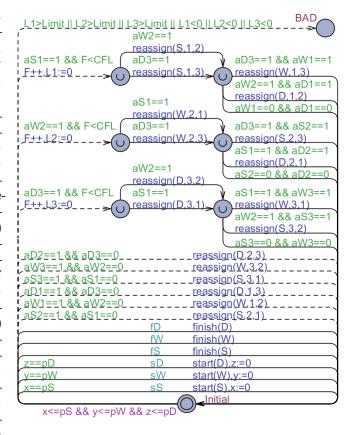

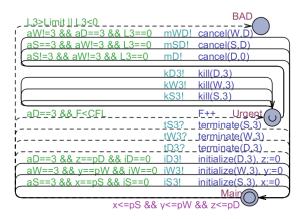

Each automaton of the concrete model represents exactly one rectangle of Figure 4. The automata synchronize using both actions and global variables. The model does not have any local variables and constants. A task automaton models initialization, killing, resumption, termination, and state information of a task on a specific core; for example, task automaton core<sub>1</sub>. S in the bottom of Figure 5 represents the activities of task S on core<sub>1</sub>. A core may fail only if the fault model allows it to fail. A core automaton models initializations and terminations of tasks on a core along with failures of the core and safety violations; for instance, core automaton core<sub>1</sub> in the middle of Figure 5 represents the activities of core core<sub>1</sub>. The service automaton in the top of Figure 5 models reallocations of the critical tasks when a core fails or recovers. In the model a failed core may recover at any time. All automata of the model are presented in the appendix.

The automata modeling cores follow the same template. For instance, automaton core<sub>1</sub> uses action kS1 to model the killing of task S on core<sub>1</sub> (edge 16 in Figure 5), kW1 to model the killing of task W on core<sub>1</sub> (edge 17), kD1 to model the killing of task D on core<sub>1</sub> (edge 18), and global variable L1 to record the current worst-case load on core<sub>1</sub> (edges 9–14,16–18); similarly, automaton core<sub>2</sub> uses action kS2 to model the killing of S on core<sub>2</sub> and global variable L2 to record the current worst-case load on core<sub>2</sub>. The automata modeling the same task—but on different cores—follow the same template.

**Task Automata** A task automaton represents two types of activities of a task on a core:

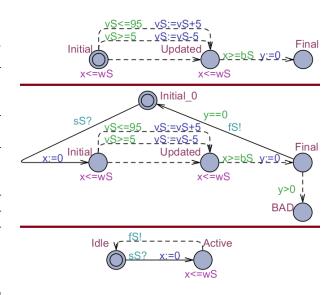

Task Life-Cycle Activities (edges 1-5) Every task can be initialized, killed, and resumed by performing controllable actions. Task terminations are modeled using uncontrollable actions because neither the scheduler nor the reconfiguration services can control the exact termination period of a task. The models are built in Uppaal Tiga [17], which displays controllable transitions as solid arrows (edges 1-4), and uncontrollable transitions as dashed arrows (edges 5-8). The duration between an initialization and the immediate termination of a task encompasses one complete execution of that task. A task can be killed and then resumed arbitrarily many times in a single execution. Initialization, killing, resumption, and termination of task S on core, is modeled by performing actions iS1 (edge 1), kS1 (edges 3-4), rS1 (edge 2), and tS1 (edge 5), respectively. Every task automaton has at least two locations: Idle and Active. The task is either killed or yet to be initialized in location Idle. Every non-idle location has an invariant to force the task to terminate within the WCET; for instance, an automaton modeling task S has invariant x≤wS to force termination, where global clock x records the amount of time passed since the last initialization of S and global constant wS stores the WCET of S. Similarly, global constant bS stores the BCET of task S. Hence, clock guard x≥bS prevents task S to terminate before the BCET (edge 5).

Task Specific Activities (edges 6-8) Task S records exactly one update of a digital speedometer (modeled as global variable vS) in an execution: vS represents the speed in multiples of five varying from zero to hundred. Boolean variable uS is 1 if and only if the speedometer is updated in the current execution of S.

Task automata  $core_1.W$  and  $core_1.D$  in the concrete model is presented in the appendix. The automata model task life-cycle activities and task specific activities of tasks W and D.

**Core Automata** A core automaton in the **concrete** model models two types of activities:

Operation-Time Activities (edges 9–14) A core automaton periodically initializes a task at its release period if the corresponding core is assigned to execute that task. Task terminates voluntarily after completing its assigned functions. A task between its initialization and termination occupies a portion of the resources. When a task terminates (resp., is initialized) on a core, the corresponding core automaton decreases (resp., increases) a variable modeling the current worst-case load. In location Main, task S is initialized by performing action iS1 (edges 9) if S is assigned to core<sub>1</sub> (aS==1), and S is not initialized yet (iS==0), and clock x hits the value of the release period of S (x==pS). Automaton core<sub>1</sub> (edge 14) receives action tS1 from task automaton core<sub>1</sub>.S (edge 5) whenever S terminates its execution on this core. Function terminate(S,1) decreases (resp., initialize(S,1) increases) variable L1, modeling the worst-case load on core<sub>1</sub>, by constant lS1, the worst-case load of task S on core core<sub>1</sub>, and resets Boolean variable iS to 0 (resp., 1), that means task S terminates (resp., is initialized).

Failure-Time Activities (edges 15-22) Core automaton core<sub>1</sub> models failures of the core by traversing an uncontrollable edge. In order to reflect our assumption on the concurrent failure limit, this edge is only admitted if the number of currently failed cores (F) is less than CFL (CFL). Location Urgent is reached from Main whenever core, fails. Urgent is one of the urgent locations<sup>4</sup>, denoted as (U) in Uppaal Tiga syntax, that means the automaton cannot spend time in this location (edges 15–21). When the core fails, the automaton instantaneously kills all tasks currently released by it—to simulate that no task can continue to run on a failed core (edges 16–18). Then the automaton instantaneously performs specific actions to broadcast a message containing the list of currently assigned tasks to that failed core: performs action mS if S is the only assigned task; action mSW if S and W are the only assigned tasks; and action mSD if S and D are the only assigned tasks (edges 19-21). To note that only task W or task D or both cannot be assigned to core core, without task S because a task (S) must be assigned to its operational primary core (core<sub>1</sub>). At runtime, the reconfiguration services use a distributed monitoring system to identify these (task) assignments because no failed core can broadcast a message. An unsafe location BAD becomes

<sup>&</sup>lt;sup>4</sup> Semantically, urgent locations are equivalent to: adding an extra clock, x, that is reset x := 0 on every incoming edge, and adding an invariant x <= 0 to the location.

Fig. 5. Automata core<sub>1</sub>.S (in the bottom), core<sub>1</sub> (in the middle), service (in the top)

reachable when the current worst-case load on core<sub>1</sub> exceeds the load limit of

core<sub>1</sub> because of the failure of some other core(s) (edge 22). This prevents the synthesis algorithm from producing a strategy that would require illegal loads.

Service Automaton A service automaton spends most of its time in observing states waiting for a fault to occur (or for a core recovery from a temporary failure). The automaton reallocates a task in two steps: (i) assigns the periodic execution of the task to a suitable operational core, and (ii) resumes the task on the assigned core if the task was initialized before the reallocation. Other than Observing all locations are committed<sup>5</sup>, denoted as  $\bigcirc$  in Uppaal Tiga syntax. They model states when reconfiguration decisions are taken, which are expected to be instantaneous and get precedence even over the urgent transitions of the other automata. Activities of the automaton can be divided into three groups described in the following.

Handling a Primary Core Failure (edges 23-37) Recall the invariant that an operating core is always assigned to execute its primary tasks, so in system, when a core (say core<sub>1</sub>) is assigned to execute only one task then it must be a primary task (S). In the model a failure message is broadcast using an action (e.g., mS, mSW, and mWD) linked to the currently assigned tasks of the failed core, instead of the name of the core. Therefore, whenever a core failing with only assignment of the periodic execution of task S (or action mS is performed) then core, the primary core of S, must be that failed core. At that point, task S is reallocated to either core<sub>2</sub> or core<sub>3</sub>. For example, location A1 is reached from location Observing when core, fails (edges 23-27); in A1 the target is reallocating S, the primary task of core<sub>1</sub>, to core core<sub>2</sub> (bottom two outgoing edges) or to core core<sub>3</sub> (top two outgoing edges). Details of reallocation depending on whether the task was initialized (and needs to be reassigned then resumed) or was yet to be initialized (and just needs to be reassigned). For instance, to reallocate task S to core<sub>2</sub>, location Observing is reentered from A1 by: (i) assigning the periodic execution of S to core<sub>2</sub> (aS:=2) if core<sub>2</sub> is operational (aW==2) and S was yet to be initialized (iS==0), or (ii) assigning the periodic execution of S to core, and resuming S on the core (by performing rS2) if core<sub>2</sub> is operational and S was initialized (iS==1).

Handling a Backup Core Failure (edges 38-52) In our example, when a core is assigned to execute two critical tasks then one of them must be a backup task of that core; hence, after such a failure at least two cores concurrently are in their failed states. The fault model does not allow all cores to fail concurrently. For instance, core<sub>1</sub> must be operational when core<sub>2</sub> and core<sub>3</sub> are in their failed states; and the executions of tasks W and D have to be assigned to core<sub>1</sub>. Location B1 is reached from Observing when a core fails that is responsible to execute both W and D or when action mWD is received (edges 48-52). Location C1 is reached from

<sup>&</sup>lt;sup>5</sup> A committed location is the same as a urgent location but after reaching a committed location the next transition must involve an outgoing edge of at least one of the committed locations of the network.

Fig. 6. Architecture of system, at runtime

B1 by assigning the periodic execution of W to the only operational core  $core_1$  and resuming W, if necessary (iW==1). Then Observing is reached by assigning the periodic execution of D to  $core_1$  and resuming D, if necessary (iD==1).

Handling a Primary Core Recovery (edges 53–67) The periodic execution of a task must be assigned to its primary core when it is operational. Therefore, a task must be reallocated from a backup core to the primary core whenever it recovers from a temporary failure. The periodic execution of task S can be assigned to a backup core (aS!=1) only if its primary core core<sub>1</sub> is in a failed state. Location G1 is reached from location Observing when core<sub>1</sub> recovers from a failure (edges 53–57). In G1 the controller has two main choices depending on the initialization condition of the task: S is yet to be initialized and needs to be only reassigned to its primary core (the bottom outgoing edge); and S is initialized on a backup core and needs to be killed (the top two outgoing edges) then to be resumed on the primary core (the outgoing edge from location H1).

## 2.4 Synthesis

We synthesize reconfiguration services in three sequential steps: 1) generate a central controller for critical tasks, 2) construct a distributed controller for each core by exclusively distributing the central controller, and 3) synthesize a reconfiguration service for each core by adding its distributed controller with a constructed monitor to broadcast its health messages and a constructed switch to suspend and reinstate its non-critical tasks. A reconfiguration service runs on a core, which can fail. Hence, fault tolerance cannot be achieved using only one central reconfiguration service. We propose for each core to execute its own reconfiguration service that has three components: a distributed controller to reallocate critical tasks, a monitoring system to observe the system's conditions, and a edge to cancel and reinstate the periodic execution of non-critical tasks. All the distributed controllers of a system differ from each other—but complement each other in a way that they all together work similarly with a central controller, which is synthesized by analyzing the timed game model of Section 2.3. Figure 6 presents the architecture of system, with the reconfiguration services at runtime.

Central Controller Synthesis We perform a controller synthesis for the monolithic model of Section 2.3 against a safety objective which states that there is a strategy to always avoid locations core<sub>1</sub>.BAD, core<sub>2</sub>.BAD, and core<sub>3</sub>.BAD. If

the property holds, the strategy—which is our central controller—is automatically synthesized by a timed game solver.

In order to obtain the most fault-tolerant controller possible, we synthesize it for the maximal concurrent-failures—limit (MCFL), the maximal value of CFL for which such a controller still exists. We use binary search to find MCFL. If MCFL is zero, no safe controller exists. The higher MCFL implies the better fault-tolerance by the reconfiguration services. The value of MCFL is strictly bounded by the total number of processing cores. Consider, for instance, configuration C1 in Table 1<sup>6</sup> where the release period, the WCET, the BCET of every task is 10, 5, and 4 time units, respectively; the worst-case load of tasks S, W, and D on core<sub>1</sub> (resp., core<sub>2</sub>, core<sub>3</sub>) are 60% (resp., 10%, 10%), 45% (resp., 80%, 5%), and 5% (resp., 5%, 85%), respectively. Configuration C1 does not have a controller for CFL 2. However, there is a controller for CFL 1. Maximal concurrent-failures—limit for system<sub>1</sub> for configuration C1 is 1 because 1 is the maximal value of CFL for which a controller exists.

**Service Synthesis** We synthesize the distributed reconfiguration service of a core by combining its distributed controller with an embedded monitor and an embedded switch.

Distributed Controller The functions of the central controller are completely and exclusively distributed into separate controllers for each core. A distributed controller is responsible for killing, reassignment, and resumption of critical tasks only on its core. A timed game represents all the possible transitions of the controller. As a result, a timed game may have non-deterministic choices for the controller. For example, in Figure 3 the controller has non-deterministic choices at system-state  $s_4$  when only  $core_2$  fails and the other two cores are operational (edges 28–32). A strategy removes non-determinism for the controller. By directing the controller to take the correct paths, a strategy plays a crucial role when in the model some paths guarantee satisfaction of a property (say reallocating task W to core<sub>3</sub> at system-state s<sub>5</sub> in Figure 3) and some paths do not (say reallocating W to core<sub>1</sub>). For example, when core<sub>2</sub> fails (edges 28–32) a strategy (or the cen $tral\ controller)\ may\ say,$  "if the system-state fulfills condition X then reallocate task W to core3, otherwise to core1"; then the distributed controller of this portion (edges 28-32) for core3 is "if the system-state fulfills condition X then reallocate task W to core;"; and the distributed controller of this portion (edges 28-32) for core, is "if the system-state does not fulfill condition X then reallocate task W to core<sub>1</sub>". Thus, deriving the distributed controllers from the central controller is a mechanical process and cannot fail.

Monitor The monitor of a reconfiguration service periodically broadcasts health messages of the corresponding core. A health message has three parts: (a) name

<sup>&</sup>lt;sup>6</sup> To show clearer impacts of different modeling aspects on the analysis, we picked some imaginary system configurations instead of some actual system configurations.

of its core, (b) currently assigned critical tasks to its core, and (c) currently initialized critical tasks on its core. A monitor periodically also receives health messages—from the other reconfiguration services—and manipulates received messages. It marks a core as a failed core if two consecutive health messages of that core are not received. The monitor identifies a core recovery when it receives a message from a previously failed core. In the same way, the monitor detects when the scheduler releases a task and when a task terminates on a core.

Switch A reconfiguration service has a static lookup table and a dynamic lookup table. The static lookup table lists the worst-case core load of every critical task (of the system) on this core and of every non-critical task assigned to this core. The dynamic lookup table keeps updated list of the assigned tasks, temporarily suspended non-critical tasks, and permanently suspended non-critical tasks. The controllers reallocate critical tasks from a failed or to a recovered core without considering the existence of non-critical tasks. The switch of a reconfiguration service (of the targeted core) suspends a set of non-critical tasks on its core using the lookup tables when the residual capacity on the core is insufficient to run the newly reallocated task safely. The distributed controllers first take necessary steps related to primary tasks of the recovered core whenever a core recovers. After that the switches reinstate the periodic executions of a set of suspended non-critical tasks on each source core where free processing capacity is revived due to the recovery. The switch permanently suspends a non-critical task when it breaches safety constraints.

#### 2.5 Manual State-Space Reduction

The scalability of our service synthesis process mostly depends on the central controller synthesis as the remaining steps are mechanical and cannot fail. The concrete model has very large state space. For example, configuration C1 in Table 1 generates a strategy of size 290,663 KB in 94.20 seconds for this model when CFL is 1, presented in Table 2. Moreover, for many configurations the solver runs out of memory during analysis, such as, C3–C5 in Table 2. Detailed and monolithic models like the concrete model are easy to construct, understand, and present. However, large state spaces make them a poor choice for analysis.

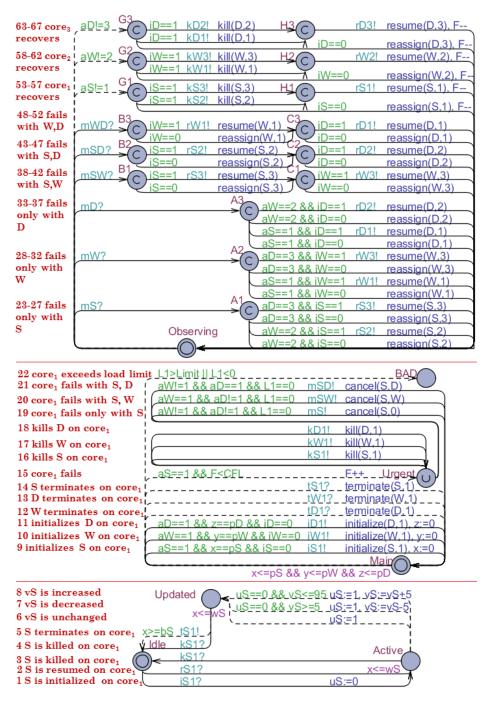

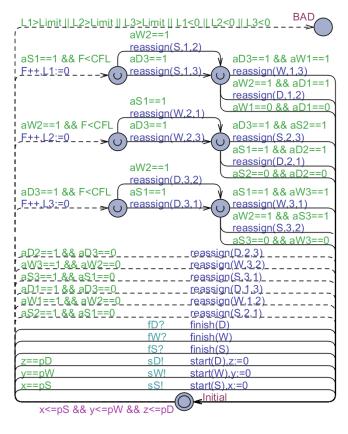

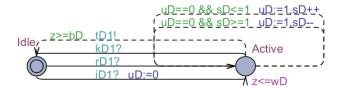

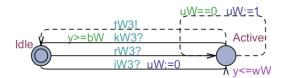

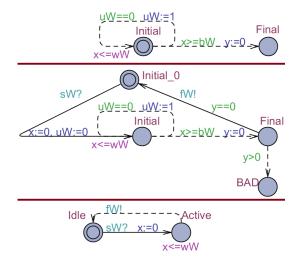

The main purpose of the strategy is to resolve non-determinism among enabled controllable transitions in a way that guarantees satisfaction of the desired property. Hence, one can abstract away every detail from a timed game model that does not contribute to the non-determinism (or to the property). For instance, task specific activities and their non-deterministic updates of the tasks, which do not have any impact on our property, can be removed from a timed game model of system<sub>1</sub>. Using such aggressive abstractions we construct the abstract model of system<sub>1</sub>. Presented in Figure 7, the model has only one automaton.

The abstract model uses all the modeling

abstractions and system parameters of Section 2.3. Explicitly it models only task initializations (edges 68-70), task terminations (edges 71-76), corefailures (edges 77–79), core recovery (edges 80– 94), and safety violations (edge 95). Like task killings and resumptions, task initializations and terminations change the load on a core; thus they play an important role in the required property (or the safety checking). The invariant is used to release or initialize the tasks periodically. While a task termination within the WCET is forced by allowing an additional controllable transition (edges 74-76). Reallocation is a function which combines task killings, reassignments, and resumptions (edges 77-94). The model uses nine Boolean variables

aS1, aW1, aD1, aS2, aW2, aD2, aS3, aW3, and aD3 to keep track the currently assigned tasks to cores: the value of aS1 (resp., aW1, aD1) is 1 when the periodic execution of task S (resp., W, D) is assigned to core core, otherwise the value is 0; similarly, aS2 (resp., aW2, aD2) is 1 if and only if the periodic execution of task S (resp., W, D) is assigned to core core. If both the concrete model and the abstract model use a variable or constant, it is used for the same purpose; for example, variable iS in both the models is used to identify when task S is initialized.

For the control problem described in this section, we constructed four different models: the concrete model as described in Section 2.3, the abstract model as described in this section, the monolithic model, and the compositional model.

| Configuration | F            | Period WCET |    | BCET         |              | Load on |                      | Load on |                      | Load on      |                      |      |              |              |    |              |    |    |

|---------------|--------------|-------------|----|--------------|--------------|---------|----------------------|---------|----------------------|--------------|----------------------|------|--------------|--------------|----|--------------|----|----|

|               | of           |             | of |              | of           |         | core <sub>1</sub> of |         | core <sub>2</sub> of |              | core <sub>3</sub> of |      |              |              |    |              |    |    |

|               |              | task        | ζ  | task         |              | task    |                      | task    |                      | task         |                      | task |              |              |    |              |    |    |

|               | $\mathbf{S}$ | W           | D  | $\mathbf{S}$ | $\mathbf{W}$ | D       | $\mathbf{S}$         | W       | D                    | $\mathbf{S}$ | W                    | D    | $\mathbf{S}$ | $\mathbf{w}$ | D  | $\mathbf{S}$ | W  | D  |

| C1            | 10           | 10          | 10 | 5            | 5            | 5       | 4                    | 4       | 4                    | 60           | 45                   | 5    | 10           | 80           | 5  | 10           | 5  | 85 |

| C2            | 10           | 10          | 10 | 5            | 5            | 5       | 0                    | 0       | 0                    | 60           | 45                   | 5    | 10           | 80           | 5  | 10           | 5  | 85 |

| C3            | 10           | 15          | 20 | 5            | 5            | 5       | 0                    | 0       | 0                    | 60           | 45                   | 5    | 10           | 80           | 5  | 10           | 5  | 85 |

| C4            | 10           | 15          | 20 | 5            | 5            | 5       | 0                    | 0       | 0                    | 60           | 35                   | 5    | 10           | 80           | 5  | 10           | 5  | 85 |

| C5            | 10           | 15          | 20 | 5            | 5            | 5       | 0                    | 0       | 0                    | 43           | 37                   | 7    | 11           | 67           | 19 | 23           | 13 | 59 |

| C6            | 10           | 15          | 20 | 5            | 5            | 5       | 0                    | 0       | 0                    | 43           | 37                   | 59   | 11           | 67           | 39 | 23           | 13 | 59 |

| C7            | 10           | 15          | 20 | 5            | 5            | 5       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C8            | 10           | 15          | 30 | 5            | 5            | 5       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C9            | 10           | 20          | 30 | 5            | 5            | 5       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C10           | 11           | 19          | 31 | 5            | 5            | 5       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C11           | 5            | 7           | 11 | 5            | 5            | 5       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C12           | 5            | 7           | 11 | 5            | 3            | 2       | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C13           | 5            | 7           | 11 | 5            | 3            | 2       | 5                    | 3       | 2                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C14           | 10           | 15          | 20 | 5            | 5            | 5       | 5                    | 5       | 5                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C15           | 10           | 15          | 20 | 5            | 7            | 11      | 5                    | 7       | 11                   | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C16           | 10           | 15          | 20 | 5            | 7            | 11      | 0                    | 0       | 0                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C17           | 10           | 15          | 20 | 7            | 7            | 7       | 7                    | 7       | 7                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C18           | 10           | 15          | 20 | 5            | 7            | 7       | 5                    | 7       | 7                    | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C19           | 10           | 15          | 20 | 7            | 7            | 11      | 7                    | 7       | 11                   | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

| C20           | 10           | 15          | 20 | 9            | 13           | 19      | 9                    | 13      | 19                   | 33           | 33                   | 33   | 33           | 33           | 33 | 33           | 33 | 33 |

Table 1. Different configurations: combinations of release period, WCET, and BCET have abstract time units; and loads are in % of the respective core

The last two models are presented in Section 3. We analyze these models with many configurations. This section discusses behaviors of the concrete and abstract models for 20 configurations of Table 1.

All the analyses and controller syntheses were performed by Uppaal Tiga-0.17 on a PC with an Intel Core i3 CPU at 2.4 GHz, 4 GB of RAM, and running 64-bit Windows 7. We compare the concrete and abstract models with respect to controller synthesis time and the strategy size. Uppaal Tiga(-0.17) generates the same (size of) strategy for the same configuration on the same machine. Controller synthesis time, on the contrary, varies a little for the same configuration on the same machine. Therefore, we synthesize a strategy for every configuration multiple times, and then take the average synthesis time for each configuration.

Experimental results of the concrete and abstract models are presented in Table 2. We have the following six observa-

| <u> </u>      | CEL |                      | <b>C</b>        | •              |      |  |  |  |  |

|---------------|-----|----------------------|-----------------|----------------|------|--|--|--|--|

| Config.       | CFL | Comparison           |                 |                |      |  |  |  |  |

| $\mathbf{of}$ |     | concre               | <b>te</b> model | abstract model |      |  |  |  |  |

| Table $2$     |     | time                 | size            | time           | size |  |  |  |  |

|               | 2   | No controller exists |                 |                |      |  |  |  |  |

| CI            | 1   | 94.20                | 290663          | 0.08           | 73   |  |  |  |  |

|               | 2   | No controller exists |                 |                |      |  |  |  |  |

| C2            | 1   | 115.71               | 296524          | 0.11           | 107  |  |  |  |  |

|               | 2   | No controller exists |                 |                |      |  |  |  |  |

| Co            | 1   | Out of               | f memory        | 0.14           | 242  |  |  |  |  |

|               | 2   | Out of               | fmomory         | 0.25           | 712  |  |  |  |  |

| 04            | 1   | Out of memory        |                 | 0.14           | 266  |  |  |  |  |

|               | 2   | Out of memor         |                 | 0.25           | 712  |  |  |  |  |

| Co            | 1   | Out of               | memory          | 0.14           | 266  |  |  |  |  |

tions from this table: **OB1A**) The abstract model improves the scalability dramatically for every configuration of Table 1. Other than aggressive abstraction, it encodes the whole model into only one automaton to avoid parallel composition, because parallel composition typically increases the size of the state space rapidly. OB2A) The larger the difference between WCET and BECT the longer the analysis time, and the sparser the strategy. Consider, for example, configuration C1 versus configuration C2, C7 versus C14, C12 versus C13, and C15 versus C16. **OB3A**) The smaller the least common multiples of release periods the smaller state space, the shorter analysis time, and the more compact strategy. Consider, for example, C2 versus C3, C8 versus C9, C9 versus C10, C10 versus C11, and so forth. For configurations C10 and C11, we use three different prime numbers as release times to get large least common multiples of the release times. As a result, for these configurations, we have sparse strategies along with long synthesis times even for the abstract model. One should check the least common multiples of the release times of a system before trying to (model and) synthesize controller for it using timed games. Unfortunately, timed games-based analytical tools

are currently not mature enough to synthesize scheduler for practical systems having large least common multiples of the release times. **OB4A**) On the other

hand, the least common multiples of the execution times have no visible impact on the analysis time or the size of the strategy; (for instance, C14 versus C15, C15 versus C17, C17 versus C18, C18 versus C19, C19 versus C20, and so forth). **OB5A)** Variations in the least common denominator of non-clock variables, such as different loads, do not have any significant impact on the analysis; (for example, C4 versus C5 and C5 versus C7). **OB6A)** Uppaal Tiga takes less time and generates a smaller strategy for a higher value for CFL; (for instance, configurations C4, C5, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19, and C20.)

Probably, the first observation **OB1A** is the most important one, which states that the scalability improves in the abstract model. Table 3 in Section 3 shows that the above observations are also true for the monolithic model and the compositional model. The MCFL of system system<sub>1</sub> depends on its configuration and model. For the concrete model, the MCFL is unknown for configurations C3, C4, C5, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19, and C20; 1 for configurations C1 and C2; and 0 for configurations C6. For the abstract model the MCFL is 2 for configurations C4, C5, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19, and C20; 1 for configurations C1, C2, and C3; and 0 for configurations C6.

#### 2.6 Discussion

We briefly discuss the handling of systems with slightly different properties. For systems with asymmetric cores, which are unable to execute some tasks on some of the cores, we simply do not model the initialization, termination, killing, reassignment, and resumption for the illegal combinations of tasks and cores. For symmetric multi-core processing (SMP) one simply has to set the same load parameters on all the cores for each task. The synthesized reconfiguration services are oblivious to the tasks having substructure (sub-tasks), if they can be consistently abstracted by a single set of parameters (WCET, BCET and load).

We have assumed that an initialized task reallocated from a failed core should resume in the same state. If this is not required, i.e., a task can start from initial state on the new core at its next release period, then the model can be simplified, by removing the edges modeling resumption. We have not investigated the synthesis process for a scheduler with a dynamic allocation yet. In the next section, we present a theoretical framework for dynamic hierarchical open systems (such as system system<sub>1</sub>) having any numbers of control hierarchies. The framework supports an automated state space reduction technique to allow timed games-based analysis for industrial dynamic hierarchical open systems.

### 3 Timed Process Automata

This section develops a model for the *automated analysis* of *safety* and *reachability* properties in industrial *time-critical systems*. To fulfill industrial requirements, we consider time-critical systems that are open (communicate with external

components), hierarchical (can be decomposed and recomposed into smaller control systems), and dynamic (the decomposition can change over time). In the section, we use *real-time systems*, meaning time-critical systems that fulfill all these features. The model also facilitates compositional modeling with reuse for different contexts.

Modeling techniques, automated analyses, and other key issues of TA are typically addressed for *static closed systems*. The application domain of TA is growing [19]. In our two projects [31,6] with an automotive manufacturer, we used different TA-based analyses to investigate the fault-tolerance of real-time systems, which are part of many large-scale safety-critical systems. During our industrial projects, we observed that continuous-time formal methods of TA may provide the most accurate analysis; however, TA are not suited for industrial real-time systems mainly because of poor *scalability*. Moreover, we found that TA may introduce cumbersome design details in a large-scale real-time system having several control hierarchies. This section extends TA to achieve better modeling support and scalability for automated analysis of hierarchical open real-time systems.

We propose timed process automata (TPA), a variant of TA, for the development of industrial hierarchical open real-time systems [32]. The proposed variant provides compositional modeling with reuse for three different contexts and automatable analysis—a system needs to be modeled and analyzed using TPA only once when copies of it are used as independent systems or multiple components of a larger system or components of different larger systems or a combination of all previous scenarios.

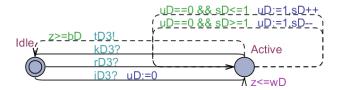

## 3.1 Processes

Timed process automata model processes in a way that each process is a dynamic hierarchical open time-critical system, which we simply call real-time system in this section. Every process hierarchically contains its active callee processes. Thus the control of a process is hierarchically shared with its active callee processes. The main thread of a process can activate callee processes via communication channels. An active process can receive any input in any state. An active callee process can deactivate itself in any state of the main thread of its caller process. An activated callee process terminates within its worst-case execution time. This section presents the syntax and the semantics of TPA.

**Timed Process Automata** Timed process automata are a variant of TIOA. Unlike a TIOA, a timed process automaton has a finite set of *start actions*  $A_s$ , a finite set of *finish actions*  $A_f$ , a final location  $l_f$ , and a finite set of *channels* C.

The set of actions  $A = A_i \oplus A_o \oplus A_s \oplus A_f$  of a timed process automaton is a disjoint union of finite sets of input actions  $A_i$ , output actions  $A_o$ , start actions  $A_s$ , and finish actions  $A_f$ . For every set of actions A, there exists a bijective mapping between its start actions  $A_s$  and finish actions  $A_f$  in such a way that for each start action  $s_N \in A_s$  there is exactly one finish action  $f_N \in A_f$ , and vice versa. These

actions can be used for starting and finishing processes associated with N. We use s and f with the name N (of another timed process automaton) as a subscript index (e.g.,  $s_N$  and  $f_N$ ) to denote a start action and a finish action, respectively. We use the same subscript to indicate *paired* actions. We write a to denote an action in general. Processes synchronize via instantaneous channels. Each timed process automaton uses the same designated symbols for its *public channel* (\*) and *caller channel* ( $\Delta$ ). We use c to denote a channel in general.

**Definition 5** A timed process automaton is a tuple  $T = (L, l_0, X, A, C, E, I, l_f)$ , where L is a finite set of locations,  $l_0 \in L$  is the initial location, X is a finite set of clocks,  $A = A_i \oplus A_o \oplus A_s \oplus A_f$  is a finite set of actions as described above, C is a finite set of channels,  $E \subseteq (L \times A \times C \setminus \{\Delta, *\} \times \Phi(X) \times 2^X \times L) \cup (L \times (A_i \cup A_o) \times \{\Delta, *\} \times \Phi(X) \times 2^X \times L)$  is a set of edges,  $I : L \to \Phi(X)$  is a total mapping from locations to invariants, and  $l_f \in L$  is a designated final location which does not have any outgoing edges to other locations and has the invariant  $I(l_f) = true$ .

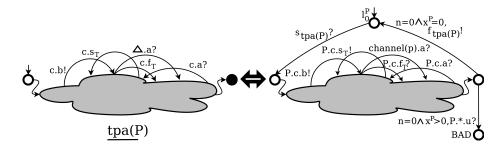

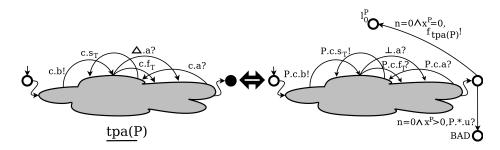

Figure 2 presents TPA Brake-by-Wire, Position, and Actuator. In the figure, each initial location has a dangling incoming edge, final locations are filled with black, and TPA names are underlined. The final location  $l_{\rm f}$  of a timed process automaton may be unreachable from the initial location (and then  $l_{\rm f}$  is not shown in the figure).

**Process Executions** Every instance of a timed process automaton is a *process*. Two processes of the same timed process automaton represent two different copies of the same system. Every process has a unique *process identifier*. A *process* is a tuple P = (id(P), tpa(P), channel(P)), where  $id(P)^7$  is the process identifier, timed process automaton tpa(P) defines the execution logic, and *caller channel* channel(P) is the private channel to communicate with the caller and the other processes which are started via the same channel. A process Q is a *callee* of P if P is the caller of Q. We use  $\bot$  to denote the caller channel of the root process. Every process P of  $tpa(P) = (L, l_0, X, A, C, E, I, l_f)$  has its own copy P.c of channel  $c \in C$ . We write P.c.a meaning that action a is performed via channel P.c.